## WINSTAR Display

# **OLED SPECIFICATION**

Model No:

WEO012864D-ZIF

### **General Specification**

| ltem             | Dimension            | Unit |  |  |  |  |

|------------------|----------------------|------|--|--|--|--|

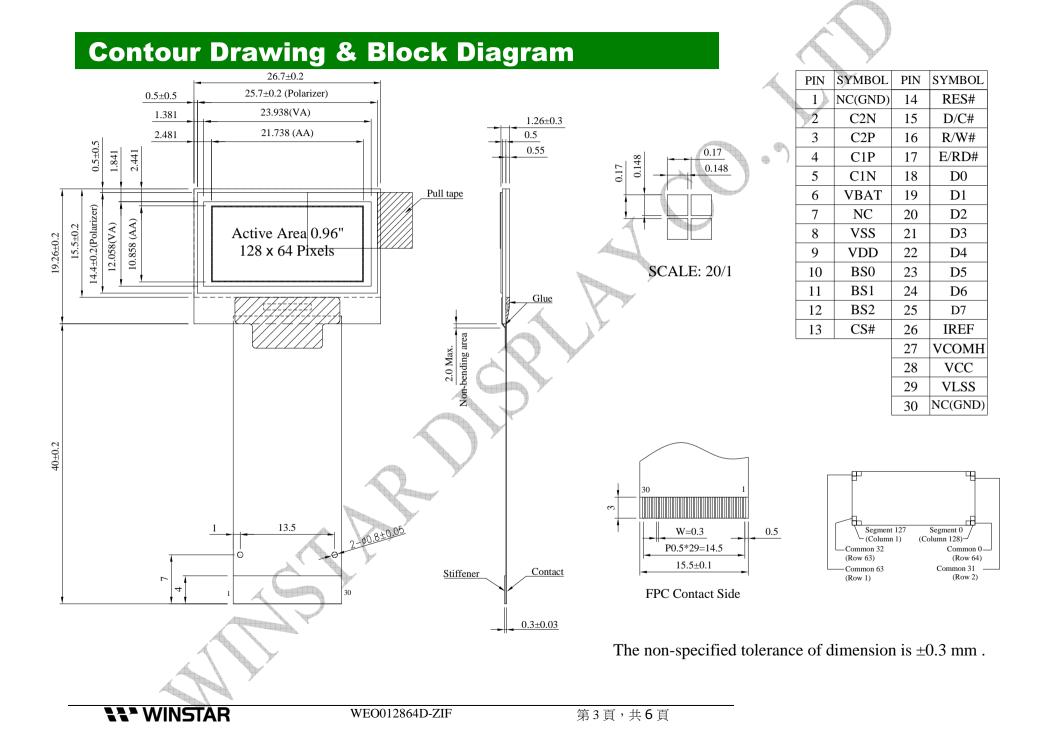

| Dot Matrix       | 128 x 64 Dots        |      |  |  |  |  |

| Module dimension | 26.70 x 19.26 x 1.26 | mm   |  |  |  |  |

| Active Area      | 21.738 x 10.858      | mm   |  |  |  |  |

| Pixel Size       | 0.148 x 0.148        | mm   |  |  |  |  |

| Pixel Pitch      | 0.17 x 0.17          | mm   |  |  |  |  |

| Display Mode     | Passive Matrix       |      |  |  |  |  |

| Display Color    | Monochrome           |      |  |  |  |  |

| Drive Duty       | 1/64 Duty            |      |  |  |  |  |

| IC               | SSD1306BZ            |      |  |  |  |  |

| Interface        | 6800,8080,SPI,I2C    |      |  |  |  |  |

| Size             | 0.96 inch            |      |  |  |  |  |

**WINSTAR**

#### **Interface Pin Function**

|                                      | No.                                                                                                                                                                                | Symbol                                  | Function                                                                   |         |                                          |           |                                          |  |  |  |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------|---------|------------------------------------------|-----------|------------------------------------------|--|--|--|--|

|                                      |                                                                                                                                                                                    |                                         | Reserved Pin (Supporting Pin)                                              |         |                                          |           |                                          |  |  |  |  |

|                                      | 1                                                                                                                                                                                  | (GND)                                   | The supporting pins can reduce the influences from stresses on the         |         |                                          |           |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         | function pins. These pins must be connected to external ground.            |         |                                          |           |                                          |  |  |  |  |

|                                      | 2                                                                                                                                                                                  | C2N                                     | Positive Terminal of the Flying Inverting Capacitor Negative Terminal of   |         |                                          |           |                                          |  |  |  |  |

|                                      | 3                                                                                                                                                                                  | C2P                                     | the Flying Boost Capacitor The charge-pump capacitors are required         |         |                                          |           |                                          |  |  |  |  |

|                                      | 4                                                                                                                                                                                  | C1P                                     | between the terminals. They must be floated when the converter is not      |         |                                          |           |                                          |  |  |  |  |

|                                      | 5                                                                                                                                                                                  | C1N                                     | used.                                                                      |         |                                          |           |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         | Power Supply for DC/DC Converter Circuit                                   |         |                                          |           |                                          |  |  |  |  |

|                                      | 6                                                                                                                                                                                  | 6 VBAT                                  |                                                                            |         |                                          |           | ouffer of the DC/DC voltage              |  |  |  |  |

| converter. It must be connected to e |                                                                                                                                                                                    |                                         |                                                                            |         |                                          |           | to external source when the converter is |  |  |  |  |

|                                      |                                                                                                                                                                                    | he converter is not used.               |                                                                            |         |                                          |           |                                          |  |  |  |  |

|                                      | 7                                                                                                                                                                                  | NC                                      | NC                                                                         |         |                                          | A         |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         | Ground of Logic Circuit                                                    |         |                                          | 1         |                                          |  |  |  |  |

|                                      | 8                                                                                                                                                                                  | VSS                                     |                                                                            |         |                                          | rence fo  | or the logic pins. It must be            |  |  |  |  |

| -                                    |                                                                                                                                                                                    |                                         | connected to external g                                                    |         | J.                                       | alan-     | · · · · · · · · · · · · · · · · · · ·    |  |  |  |  |

|                                      | 9                                                                                                                                                                                  | VDD                                     | Power Supply for Logic                                                     |         |                                          |           |                                          |  |  |  |  |

|                                      | Ŭ                                                                                                                                                                                  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                                                            |         | 4900                                     | pe conne  | ected to external source.                |  |  |  |  |

|                                      | 10                                                                                                                                                                                 | <b>D</b> 00                             | Communicating Protoc                                                       |         |                                          | Y.M.      |                                          |  |  |  |  |

|                                      | 10                                                                                                                                                                                 | BS0                                     | These pins are MCU in                                                      | terfac  | e select                                 | ion inpu  | it. See the                              |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         | following table:                                                           |         |                                          |           |                                          |  |  |  |  |

|                                      | 11                                                                                                                                                                                 | BS1                                     |                                                                            | BS0     | BS1                                      | BS2       |                                          |  |  |  |  |

|                                      | 11                                                                                                                                                                                 | 001                                     | I2C<br>3-wire SPI                                                          | 0       | 1                                        | 0         |                                          |  |  |  |  |

| -                                    |                                                                                                                                                                                    |                                         | 4-wire SPI                                                                 | 0       | õ                                        | ŏ         |                                          |  |  |  |  |

|                                      | 12                                                                                                                                                                                 | BS2                                     | 8-bit 68XX Parallel                                                        | 0       | 0                                        | 1         |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         | 8-bit 80XX Parallel                                                        | 0       | 1                                        | 1         |                                          |  |  |  |  |

| -                                    |                                                                                                                                                                                    |                                         | Chip Select                                                                |         |                                          |           |                                          |  |  |  |  |

|                                      | 13                                                                                                                                                                                 | CS#                                     | This pin is the chip sele                                                  | ect inp | ut. The                                  | chip is e | enabled for MCU                          |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         | communication only wh                                                      | nen CS  | S# is pu                                 | lled low. |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         | Power Reset for Control                                                    | oller a | nd Drive                                 | ər        |                                          |  |  |  |  |

|                                      | 14                                                                                                                                                                                 | RES#                                    | This pin is reset signal                                                   | input.  | When t                                   | he pin is | s low, initialization of the chip        |  |  |  |  |

|                                      |                                                                                                                                                                                    | A                                       | is executed.                                                               |         |                                          |           |                                          |  |  |  |  |

|                                      | 4                                                                                                                                                                                  |                                         | Data/Command Control                                                       |         |                                          |           |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         |                                                                            |         |                                          |           | n the pin is pulled high, the            |  |  |  |  |

|                                      | input at D7~D0 is treated as display data.<br>When the pin is pulled low, the input at D7~D0 will be transferred command register. For detail relationship to MCU interface signal |                                         |                                                                            |         |                                          |           |                                          |  |  |  |  |

| A                                    |                                                                                                                                                                                    |                                         |                                                                            |         |                                          |           |                                          |  |  |  |  |

| × \                                  |                                                                                                                                                                                    |                                         |                                                                            |         |                                          |           |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    | 2/0//                                   | please refer to the Timing Characteristics Diagrams.                       |         |                                          |           |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         |                                                                            |         | d serial interface mode is selected, the |           |                                          |  |  |  |  |

| -48                                  | data at SDIN is treated as data. When it is pulled low, the data at SI                                                                                                             |                                         |                                                                            |         |                                          |           |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    |                                         | will be transferred to the command register. In I2C mode, this pin acts as |         |                                          |           |                                          |  |  |  |  |

|                                      |                                                                                                                                                                                    | SA0 for slave address selection.        |                                                                            |         |                                          |           |                                          |  |  |  |  |

| 16    | R/W#        | Read/Write Select or Write<br>This pin is MCU interface input. When interfacing to a 68XX-series<br>microprocessor, this pin will be used as Read/Write (R/W#) selection<br>input. Pull this pin to "High" for read mode and pull it to "Low" for write<br>mode.<br>When 80XX interface mode is selected, this pin will be the Write (WR#)<br>input. Data write operation is initiated when this pin is pulled low and the<br>CS# is pulled low.    |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17    | E/RD#       | Read/Write Enable or Read<br>This pin is MCU interface input. When interfacing to a 68XX-series<br>microprocessor, this pin will be used as the Enable (E) signal. Read/write<br>operation is initiated when this pin is pulled high and the CS# is pulled<br>low.<br>When connecting to an 80XX-microprocessor, this pin receives the Read<br>(RD#) signal. Data read operation is initiated when this pin is pulled low<br>and CS# is pulled low. |

| 18~25 | D0~D7       | Host Data Input/Output Bus<br>These pins are 8-bit bi-directional data bus to be connected to the<br>microprocessor's data bus. When serial mode is selected, D1 will be the<br>serial data input SDIN and D0 will be the serial clock input SCLK. When<br>I2C mode is selected, D2 & D1 should be tired together and serve as<br>SDAout & SDAin in application and D0 is the serial clock input SCL.                                               |

| 26    | IREF        | Current Reference for Brightness Adjustment<br>This pin is segment current reference pin. A resistor should be connected<br>between this pin and VSS. Set the current lower than 12.5µA.                                                                                                                                                                                                                                                            |

| 27    | VCOMH       | Voltage Output High Level for COM Signal<br>This pin is the input pin for the voltage output high level for COM signals.<br>A capacitor should be connected between this pin and VSS.                                                                                                                                                                                                                                                               |

| 28    | vcc         | Power Supply for OEL Panel<br>This is the most positive voltage supply pin of the chip. A stabilization<br>capacitor should be connected between this pin and VSS when the<br>converter is used. It must be connected to external source when the<br>converter is not used.                                                                                                                                                                         |

| 29    | VLSS        | Ground of Analog Circuit<br>This is an analog ground pin. It should be connected to VSS externally.                                                                                                                                                                                                                                                                                                                                                 |

| 30    | NC<br>(GND) | Reserved Pin (Supporting Pin)<br>The supporting pins can reduce the influences from stresses on the<br>function pins. These pins must be connected to external ground.                                                                                                                                                                                                                                                                              |

|       | 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### **Absolute Maximum Ratings**

| Symbol | Min               | Мах                     | Unit                                 |

|--------|-------------------|-------------------------|--------------------------------------|

| VDD    | 0                 | 4.0                     | V                                    |

| VCC    | 0                 | 15.0                    | V                                    |

| TOP    | -40               | +80                     | °C                                   |

| TSTG   | -40               | +85                     | °C                                   |

|        | VDD<br>VCC<br>TOP | VDD 0   VCC 0   TOP -40 | VDD 0 4.0   VCC 0 15.0   TOP -40 +80 |

#### **Electrical Characteristics**

#### **DC Electrical Characteristics**

| ltem                                          | Symbol | Condition | Min     | Тур  | Max     | Unit |

|-----------------------------------------------|--------|-----------|---------|------|---------|------|

| Supply Voltage for Logic                      | VDD    |           | 2.8     | 3.0  | 3.3     | V    |

| Supply Voltage for Display                    | VCC    | X         | 11.5    | 12.0 | 12.5    | V    |

| Input High Volt.                              | VIH    | L,        | 0.8×VDD | _    | VDDIO   | V    |

| Input Low Volt.                               | VIL    | _         | 0       | _    | 0.2×VDD | V    |

| Output High Volt.                             | VOH    | _         | 0.9×VDD | _    | VDDIO   | V    |

| Output Low Volt.                              | VOL    | _         | 0       | _    | 0.1×VDD | V    |

| Operating Current for VCC<br>(50% display ON) | ICC    |           |         | 19.5 | 25.0    | mA   |