# **OLED DISPLAY SPECIFICATION**

# 曜凌光電股份有限公司 Raystar Optronics, Inc.

T: +886-4-2565-0761 | F: +886-4-2565-0760

salescontact@raystar-optronics.com | www.raystar-optronics.com

#### **REX012864U**

### **General Specification**

The features is described as follow:

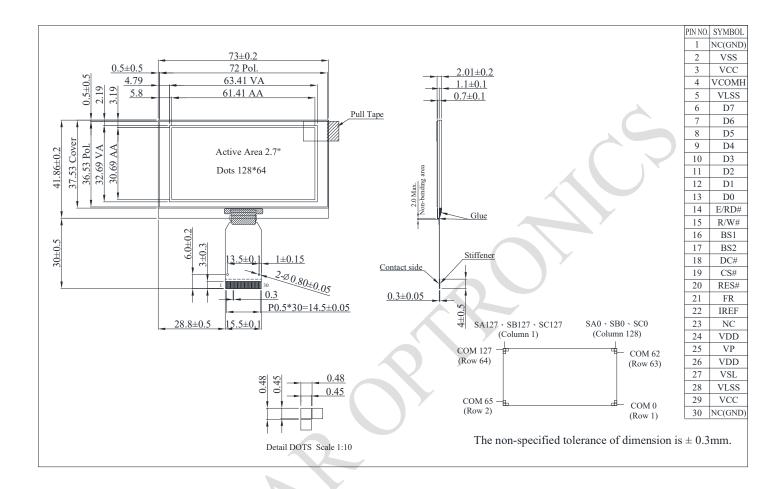

■ Dot Matrix: 128 x 64

■ Module Dimension: 73.0 x 41.86 x 2.01 mm

Active Area: 61.41 x 30.69 mm

■ Pixel Size: 0.45 x 0.45 mm

■ Pixel Pitch: 0.48 x 0.48 mm

Display Mode: Passive Matrix

Display Color: Monochrome

■ Drive Duty: 1/64 Duty

Gray Scale: 4 bits

■ Interface: 8-bits 6800 and 8080 parallel, 4-line SPI, I2C

■ IC: SSD1357

■ Size: 2.7-inch

#### **Interface Pin Function**

| Symbol      | Function                                                                    |  |  |  |  |

|-------------|-----------------------------------------------------------------------------|--|--|--|--|

| 10 (0) 10 ) |                                                                             |  |  |  |  |

| , ,         | No connection.                                                              |  |  |  |  |

| VSS         | Ground pin. It must be connected to external ground.                        |  |  |  |  |

|             | Power supply for panel driving voltage. This is also the most positive      |  |  |  |  |

| VCC         | power voltage supply pin.                                                   |  |  |  |  |

|             | A capacitor should be connected between this pin and VSS.                   |  |  |  |  |

| VCOMH       | COM signal deselected voltage level.                                        |  |  |  |  |

| VCOIVIII    | A capacitor should be connected between this pin and VSS.                   |  |  |  |  |

| VLSS        | Analog system ground pin. It must be connected to external ground.          |  |  |  |  |

|             | These pins are bi-directional data bus connecting to the MCU data bus.      |  |  |  |  |

|             | Unused pins are recommended to tie LOW.                                     |  |  |  |  |

| D7D0        | When serial interface mode is selected, D0 will be the serial clock input:  |  |  |  |  |

| רט~וט       | SCLK; D1 will be the serial data input: SDIN and D2 should be kept NC.      |  |  |  |  |

|             | When I2C mode is selected, D2, D1 should be tied together and serve as      |  |  |  |  |

|             | SDAout, SDAin in application and D0 is the serial clock input, SCL.         |  |  |  |  |

|             | This pin is MCU interface input.                                            |  |  |  |  |

|             | When 6800 interface mode is selected, this pin will be used as the Enable   |  |  |  |  |

|             | (E) signal.                                                                 |  |  |  |  |

| 4           | Read/write operation is initiated when this pin is pulled HIGH and the chip |  |  |  |  |

| E/PD#       | is selected.                                                                |  |  |  |  |

| E/ND#       | When 8080 interface mode is selected, this pin receives the Read (RD#)      |  |  |  |  |

|             | signal. Read operation is initiated when this pin is pulled LOW and the     |  |  |  |  |

|             | chip is selected.                                                           |  |  |  |  |

|             | When serial or I2C interface is selected, this pin must be connected to     |  |  |  |  |

|             | VSS.                                                                        |  |  |  |  |

|             | This pin is read / write control input pin connecting to the MCU interface. |  |  |  |  |

| R/W#        | When 6800 interface mode is selected, this pin will be used as              |  |  |  |  |

|             | Read/Write (R/W#) selection input. Read mode will be carried out when       |  |  |  |  |

|             | this pin is pulled HIGH and write mode when LOW.                            |  |  |  |  |

|             | C(GND) VSS VCC /COMH VLSS D7~D0  E/RD#                                      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |      | When 8080 interface m                                                        | ode is sele | ected, this p | oin will be the Write (WR#) |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|------------------------------------------------------------------------------|-------------|---------------|-----------------------------|--|--|

| chip is selected. When serial or I2C interface is selected, this pin must be connected to VSS.  Communicating Protocol Select. These pins are MCU interface selection input. See the following table:    BS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      | input. Data write operation is initiated when this pin is pulled LOW and the |             |               |                             |  |  |

| VSS.  Communicating Protocol Select. These pins are MCU interface selection input. See the following table:    BS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |      |                                                                              |             |               |                             |  |  |

| VSS.  Communicating Protocol Select. These pins are MCU interface selection input. See the following table:    BS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |      | ·                                                                            |             |               |                             |  |  |

| These pins are MCU interface selection input. See the following table:    BS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |      |                                                                              |             |               |                             |  |  |

| These pins are MCU interface selection input. See the following table:    BS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |      | Communicating Protoco                                                        | ol Select   |               |                             |  |  |

| BS1   BS2   I2C   1   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      |                                                                              |             |               |                             |  |  |

| 18 BS1 BS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |      | These pine are mee in                                                        |             |               | la. Goo are reneming table. |  |  |

| 4-wire Serial  8-bit 8080 Parallel  1 1  8-bit 6800 Parallel  7 This pin is Data/Command control pin connecting to the MCU.  When the pin is pulled HIGH, the data at D[7:0] will be interpreted as data.  When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register.  In I2C mode, this pin acts as SA0 for slave address selection.  This pin is the chip select input connecting to the MCU.  The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input.  When the pin is pulled LOW, initialization of the chip is executed.  Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin | 16 | BS1  | I2C                                                                          |             |               |                             |  |  |

| 8-bit 8080 Parallel 1 1  8-bit 6800 Parallel 0 1  This pin is Data/Command control pin connecting to the MCU. When the pin is pulled HIGH, the data at D[7:0] will be interpreted as data. When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register. In I2C mode, this pin acts as SA0 for slave address selection.  This pin is the chip select input connecting to the MCU. The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input. When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect. It should be kept NC if it is not used.  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin                       | 17 | BS2  |                                                                              |             |               |                             |  |  |

| This pin is Data/Command control pin connecting to the MCU. When the pin is pulled HIGH, the data at D[7:0] will be interpreted as data. When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register. In I2C mode, this pin acts as SA0 for slave address selection.  This pin is the chip select input connecting to the MCU. The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input. When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect. It should be kept NC if it is not used.  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin                                                                         |    |      |                                                                              |             |               |                             |  |  |

| This pin is Data/Command control pin connecting to the MCU. When the pin is pulled HIGH, the data at D[7:0] will be interpreted as data. When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register. In I2C mode, this pin acts as SA0 for slave address selection.  This pin is the chip select input connecting to the MCU. The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input. When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect. It should be kept NC if it is not used.  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin  Reserved Pin                                                           |    |      |                                                                              |             | 1             | <i>Y</i>                    |  |  |

| When the pin is pulled HIGH, the data at D[7:0] will be interpreted as data.  When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register.  In I2C mode, this pin acts as SA0 for slave address selection.  This pin is the chip select input connecting to the MCU.  The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input.  When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin                                                                                                                                |    |      |                                                                              |             |               |                             |  |  |

| data. When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register. In I2C mode, this pin acts as SA0 for slave address selection.  This pin is the chip select input connecting to the MCU. The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input. When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect. It should be kept NC if it is not used.  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                            |    |      |                                                                              |             |               |                             |  |  |

| When the pin is pulled LOW, the data at D[7:0] will be transferred to a command register.  In I2C mode, this pin acts as SA0 for slave address selection.  This pin is the chip select input connecting to the MCU.  The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input.  When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                              |    |      | When the pin is pulled HIGH, the data at D[7:0] will be interpreted as       |             |               |                             |  |  |

| command register.  In I2C mode, this pin acts as SA0 for slave address selection.  This pin is the chip select input connecting to the MCU.  The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input.  When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect. It should be kept NC if it is not used.  REF  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                  | 18 | D/C# | data.                                                                        |             |               |                             |  |  |

| In I2C mode, this pin acts as SA0 for slave address selection.  This pin is the chip select input connecting to the MCU.  The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input.  When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect. It should be kept NC if it is not used.  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                          |    |      | When the pin is pulled LOW, the data at D[7:0] will be transferred to a      |             |               |                             |  |  |

| This pin is the chip select input connecting to the MCU.  The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input.  When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                         |    |      | command register.                                                            |             |               |                             |  |  |

| The chip is enabled for MCU communication only when CS# is pulled LOW (active LOW).  This pin is reset signal input.  When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect. It should be kept NC if it is not used.  This pin is the segment output current reference pin. IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |      | In I2C mode, this pin acts as SA0 for slave address selection.               |             |               |                             |  |  |

| LOW (active LOW).  This pin is reset signal input.  When the pin is pulled LOW, initialization of the chip is executed.  Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | CS#  | This pin is the chip select input connecting to the MCU.                     |             |               |                             |  |  |

| This pin is reset signal input.  When the pin is pulled LOW, initialization of the chip is executed.  Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19 |      | The chip is enabled for MCU communication only when CS# is pulled            |             |               |                             |  |  |

| 20 RES# When the pin is pulled LOW, initialization of the chip is executed. Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      | LOW (active LOW).                                                            |             |               |                             |  |  |

| Keep this pin pull HIGH during normal operation.  This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |      | This pin is reset signal i                                                   | nput.       |               |                             |  |  |

| This pin outputs RAM write synchronization signal. Proper timing between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 |      | When the pin is pulled LOW, initialization of the chip is executed.          |             |               |                             |  |  |

| between MCU data writing and frame display timing can be achieved to prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      | Keep this pin pull HIGH during normal operation.                             |             |               |                             |  |  |

| prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | FR   | This pin outputs RAM write synchronization signal. Proper timing             |             |               |                             |  |  |

| prevent tearing effect.  It should be kept NC if it is not used.  This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21 |      | between MCU data writing and frame display timing can be achieved to         |             |               |                             |  |  |

| This pin is the segment output current reference pin.  IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21 |      | prevent tearing effect.                                                      |             |               |                             |  |  |

| IREF IREF IREF IREF is supplied externally.  Reserved Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |      | It should be kept NC if it is not used.                                      |             |               |                             |  |  |

| IREF is supplied externally.  Reserved Pin  N.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22 | IDEE | This pin is the segment output current reference pin.                        |             |               |                             |  |  |

| 23   N.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | IKEF | IREF is supplied externally.                                                 |             |               |                             |  |  |

| The N.C. pin between function pins is reserved for compatible and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22 | N C  | Reserved Pin                                                                 |             |               |                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ۷۵ | N.C. | The N.C. pin between f                                                       | unction pir | ns is reserv  | red for compatible and      |  |  |

|    |         | flexible design.                                                       |  |

|----|---------|------------------------------------------------------------------------|--|

| 24 | VDD     | Power supply pin for core logic operation. A capacitor should be       |  |

| 24 | VDD     | connected between this pin and VSS.                                    |  |

|    |         | This pin is the segment pre-charge voltage reference pin.              |  |

| 25 | VP      | A capacitor can be connected between this pin and VSS to improve       |  |

| 25 |         | vision performance.                                                    |  |

|    |         | No external power supply is allowed to connect to this pin.            |  |

| 26 | VDD     | Power supply pin for core logic operation. A capacitor should be       |  |

| 26 | VDD     | connected between this pin and VSS.                                    |  |

| 27 | VSL     | This is segment voltage (output low level) reference pin.              |  |

| 27 | VSL     | This pin has to connect with resistor and diode to ground.             |  |

| 28 | VLSS    | Analog system ground pin. It must be connected to external ground.     |  |

|    |         | Power supply for panel driving voltage. This is also the most positive |  |

| 29 | VCC     | power voltage supply pin.                                              |  |

|    |         | A capacitor should be connected between this pin and VSS.              |  |

| 30 | NC(GND) | No connection                                                          |  |

#### **Contour Drawing**

## **Absolute Maximum Ratings**

| Parameter                  | Symbol | Min  | Max  | Unit |

|----------------------------|--------|------|------|------|

| Supply Voltage for Logic   | VDD    | -0.3 | 4.0  | V    |

| Supply Voltage for Display | VCC    | 0    | 19.0 | V    |

| Operating Temperature      | TOP    | -40  | +80  | °C   |

| Storage Temperature        | TSTG   | -40  | +85  | °C   |

# **Electrical Characteristics DC Electrical Characteristics**

| Item                       | Symbol | Condition  | Min     | Тур  | Max     | Unit |

|----------------------------|--------|------------|---------|------|---------|------|

| Supply Voltage for Logic   | VDD    |            | 1.65    | 3.0  | 3.3     | V    |

| Supply Voltage for Display | VCC    | (-)        | 8.0     | 10.0 | 10.5    | V    |

| High Level Input           | VIH    |            | 0.8×VDD | _    | VDD     | V    |

| Low Level Input            | VIL    | _          | _       | _    | 0.2×VDD | V    |

| High Level Output          | VOH    | _          | 0.9×VDD | _    | VDD     | V    |

| Low Level Output           | VOL    | _          | _       | _    | 0.1×VDD | V    |

| Display 50% Pixel on       | ICC    | VCC =10.0V | _       | 46   | 69      | mA   |